- 您现在的位置:买卖IC网 > Sheet目录3833 > PIC16LF84A-04I/SS (Microchip Technology)IC MCU FLASH 1KX14 EE 20SSOP

Micrel, Inc.

KSZ8851SNL/SNLI

August 2009

56

M9999-083109-2.0

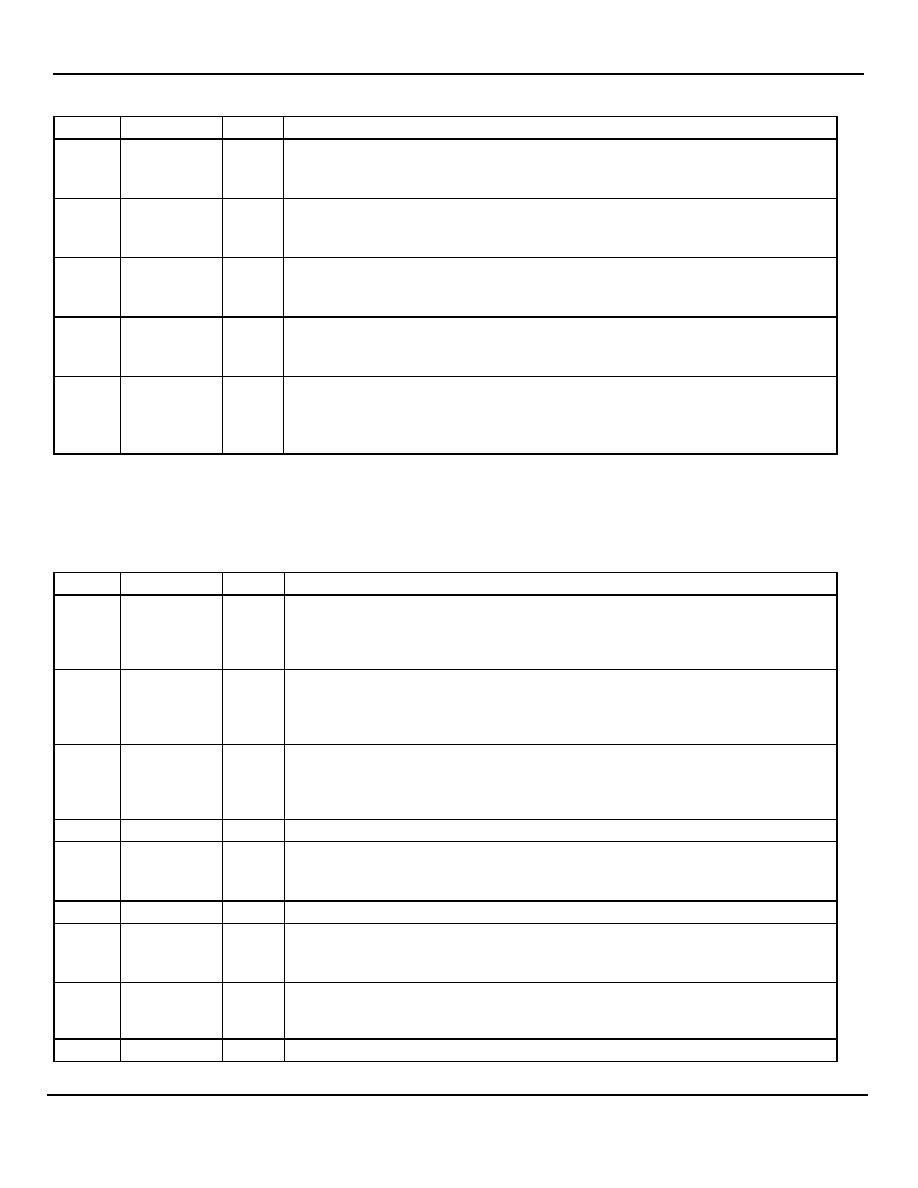

Bit

Default Value

R/W

Description

4

0x0

RW

RXMPDIE Receive Magic Packet Detect Interrupt Enable

When this bit is set, the Receive magic packet detect interrupt is enabled.

When this bit is reset, the Receive magic packet detect interrupt is disabled.

3

0x0

RW

LDIE Linkup Detect Interrupt Enable

When this bit is set, the wake-up from linkup detect interrupt is enabled.

When this bit is reset, the linkup detect interrupt is disabled.

2

0x0

RW

EDIE Energy Detect Interrupt Enable

When this bit is set, the wake-up from energy detect interrupt is enabled.

When this bit is reset, the energy detect interrupt is disabled.

1

0x0

RW

SPIBEIE SPI Bus Error Interrupt Enable

When this bit is set, the SPI bus error interrupt is enabled.

When this bit is reset, the SPI bus error interrupt is disabled.

0

0x0

RW

DEDIE Delay Energy Detect Interrupt Enable

When this bit is set, the delay energy detect interrupt is enabled.

When this bit is reset, the delay energy detect interrupt is disabled.

Note: the delay energy detect interrupt till device is ready for host access.

Interrupt Status Register (0x92 – 0x93): ISR

This register contains the status bits for all QMU and other interrupt sources.

When the corresponding enable bit is set, it causes the interrupt pin to be asserted.

This register is usually read by the host CPU and device drivers during interrupt service routine or polling. The register

bits are not cleared when read. The user has to write “1” to clear.

Bit

Default Value

R/W

Description

15

0x0

RO

(W1C)

LCIS Link Change Interrupt Status

When this bit is set, it indicates that the link status has changed from link up to link down,

or link down to link up.

This edge-triggered interrupt status is cleared by writing 1 to this bit.

14

0x0

RO

(W1C)

TXIS Transmit Interrupt Status

When this bit is set, it indicates that the TXQ MAC has transmitted at least a frame on the

MAC interface and the QMU TXQ is ready for new frames from the host.

This edge-triggered interrupt status is cleared by writing 1 to this bit.

13

0x0

RO

(W1C)

RXIS Receive Interrupt Status

When this bit is set, it indicates that the QMU RXQ has received at least a frame from the

MAC interface and the frame is ready for the host CPU to process.

This edge-triggered interrupt status is cleared by writing 1 to this bit.

12

0x0

RO

Reserved

11

0x0

RO

(W1C)

RXOIS Receive Overrun Interrupt Status

When this bit is set, it indicates that the Receive Overrun status has occurred.

This edge-triggered interrupt status is cleared by writing 1 to this bit.

10

0x0

RO

Reserved

9

0x1

RO

(W1C)

TXPSIS Transmit Process Stopped Interrupt Status

When this bit is set, it indicates that the Transmit Process has stopped.

This edge-triggered interrupt status is cleared by writing 1 to this bit.

8

0x1

RO

(W1C)

RXPSIS Receive Process Stopped Interrupt Status

When this bit is set, it indicates that the Receive Process has stopped.

This edge-triggered interrupt status is cleared by writing 1 to this bit.

7

0x0

RO

Reserved

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

5176916-1

HIGH CURRENT DRAWER 24P

PIC18F2520-I/SP

IC MCU FLASH 16KX16 28-DIP

PIC18F86J65-I/PT

IC PIC MCU FLASH 48KX16 80TQFP

PIC32MX320F064H-40I/MR

IC PIC MCU FLASH 64KB 64-QFN

PIC18F4423-I/P

IC PIC MCU FLASH 8KX16 40DIP

PIC18LF8390-I/PT

IC PIC MCU FLASH 4KX16 80TQFP

PIC18F2455-I/SO

IC PIC MCU FLASH 12KX16 28SOIC

TS87C51RD2-VCL

IC MCU 8051 OTP 64K 5V 68PLCC

相关代理商/技术参数

PIC16LF84A-04I/SS

制造商:Microchip Technology Inc 功能描述:8BIT FLASH MCU SMD 16LF84 SSOP28

PIC16LF84AT-04/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84AT-04/SS

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84AT-04I/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84AT-04I/SS

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84T-04/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84T-04I/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF870-I/SO

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT